|

Defines |

| #define | IEEE80211_ADDR_LEN 6 |

| #define | HAL_OK 0 |

| #define | HAL_EINVAL 1 |

| #define | HAL_EINPROGRESS EINPROGRESS |

| #define | HAL_NUM_TX_QUEUES 10 |

| #define | TXQ_FLAG_TXINT_ENABLE 0x0001 |

| #define | TXQ_FLAG_TXDESCINT_ENABLE 0x0002 |

| #define | TXQ_FLAG_BACKOFF_DISABLE 0x0004 |

| #define | TXQ_FLAG_COMPRESSION_ENABLE 0x0008 |

| #define | TXQ_FLAG_RDYTIME_EXP_POLICY_ENABLE 0x0010 |

| #define | TXQ_FLAG_FRAG_BURST_BACKOFF_ENABLE 0x0020 |

| #define | TXQ_FLAG_POST_FR_BKOFF_DIS 0x0040 |

| #define | TXQ_FLAG_TXEOLINT_ENABLE 0x0080 |

| #define | AR5K_CCK_SIFS_TIME 10 |

| #define | AR5K_CCK_PREAMBLE_BITS 144 |

| #define | AR5K_CCK_PLCP_BITS 48 |

| #define | AR5K_CCK_NUM_BITS(_frmlen) (_frmlen << 3) |

| #define | AR5K_CCK_PHY_TIME(_sp) |

| #define | AR5K_CCK_TX_TIME(_kbps, _frmlen, _sp) |

| #define | AR5K_OFDM_SIFS_TIME 16 |

| #define | AR5K_OFDM_PREAMBLE_TIME 20 |

| #define | AR5K_OFDM_PLCP_BITS 22 |

| #define | AR5K_OFDM_SYMBOL_TIME 4 |

| #define | AR5K_OFDM_NUM_BITS(_frmlen) (AR5K_OFDM_PLCP_BITS + (_frmlen << 3)) |

| #define | AR5K_OFDM_NUM_BITS_PER_SYM(_kbps) |

| #define | AR5K_OFDM_NUM_BITS(_frmlen) (AR5K_OFDM_PLCP_BITS + (_frmlen << 3)) |

| #define | AR5K_OFDM_NUM_SYMBOLS(_kbps, _frmlen) howmany(AR5K_OFDM_NUM_BITS(_frmlen), AR5K_OFDM_NUM_BITS_PER_SYM(_kbps)) |

| #define | AR5K_OFDM_TX_TIME(_kbps, _frmlen) |

| #define | AR5K_TURBO_SIFS_TIME 8 |

| #define | AR5K_TURBO_PREAMBLE_TIME 14 |

| #define | AR5K_TURBO_PLCP_BITS 22 |

| #define | AR5K_TURBO_SYMBOL_TIME 4 |

| #define | AR5K_TURBO_NUM_BITS(_frmlen) (AR5K_TURBO_PLCP_BITS + (_frmlen << 3)) |

| #define | AR5K_TURBO_NUM_BITS_PER_SYM(_kbps) |

| #define | AR5K_TURBO_NUM_BITS(_frmlen) (AR5K_TURBO_PLCP_BITS + (_frmlen << 3)) |

| #define | AR5K_TURBO_NUM_SYMBOLS(_kbps, _frmlen) |

| #define | AR5K_TURBO_TX_TIME(_kbps, _frmlen) |

| #define | AR5K_XR_SIFS_TIME 16 |

| #define | AR5K_XR_PLCP_BITS 22 |

| #define | AR5K_XR_SYMBOL_TIME 4 |

| #define | AR5K_XR_PREAMBLE_TIME(_kbps) (((_kbps) < 1000) ? 173 : 76) |

| #define | AR5K_XR_NUM_BITS_PER_SYM(_kbps) |

| #define | AR5K_XR_NUM_BITS(_frmlen) (AR5K_XR_PLCP_BITS + (_frmlen << 3)) |

| #define | AR5K_XR_NUM_SYMBOLS(_kbps, _frmlen) howmany(AR5K_XR_NUM_BITS(_frmlen), AR5K_XR_NUM_BITS_PER_SYM(_kbps)) |

| #define | AR5K_XR_TX_TIME(_kbps, _frmlen) |

| #define | HAL_RX_FILTER_UCAST 0x00000001 |

| #define | HAL_RX_FILTER_MCAST 0x00000002 |

| #define | HAL_RX_FILTER_BCAST 0x00000004 |

| #define | HAL_RX_FILTER_CONTROL 0x00000008 |

| #define | HAL_RX_FILTER_BEACON 0x00000010 |

| #define | HAL_RX_FILTER_PROM 0x00000020 |

| #define | HAL_RX_FILTER_PROBEREQ 0x00000080 |

| #define | HAL_RX_FILTER_PHYERR 0x00000100 |

| #define | HAL_RX_FILTER_PHYRADAR 0x00000200 |

| #define | HAL_BEACON_PERIOD 0x0000ffff |

| #define | HAL_BEACON_ENA 0x00800000 |

| #define | HAL_BEACON_RESET_TSF 0x01000000 |

| #define | bs_nexttbtt bs_next_beacon |

| #define | bs_intval bs_interval |

| #define | bs_nextdtim bs_next_dtim |

| #define | bs_bmissthreshold bs_bmiss_threshold |

| #define | bs_sleepduration bs_sleep_duration |

| #define | bs_dtimperiod bs_dtim_period |

| #define | CTRY_DEFAULT 0 |

| #define | CHANNEL_2GHZ 0x0080 |

| #define | CHANNEL_OFDM 0x0040 |

| #define | CHANNEL_TURBO 0x0010 |

| #define | CHANNEL_108G (CHANNEL_2GHZ|CHANNEL_OFDM|CHANNEL_TURBO) |

| #define | AR5K_KEYVAL_LENGTH_40 5 |

| #define | AR5K_KEYVAL_LENGTH_104 13 |

| #define | AR5K_KEYVAL_LENGTH_128 16 |

| #define | AR5K_KEYVAL_LENGTH_MAX AR5K_KEYVAL_LENGTH_128 |

| #define | HAL_TXQ_USEDEFAULT ((u_int32_t) -1) |

| #define | HAL_RSSI_EP_MULTIPLIER (1<<7) |

| #define | AR5K_ASSERT_ENTRY(_e, _s) |

| #define | AR5K_MAX_RATES 32 |

| #define | r_valid valid |

| #define | r_phy phy |

| #define | r_rate_kbps rateKbps |

| #define | r_rate_code rateCode |

| #define | r_short_preamble shortPreamble |

| #define | r_dot11_rate dot11Rate |

| #define | r_control_rate controlRate |

| #define | rt_rate_count rateCount |

| #define | rt_rate_code_index rateCodeToIndex |

| #define | rt_info info |

| #define | AR5K_RATES_11A |

| #define | AR5K_RATES_11B |

| #define | AR5K_RATES_11G |

| #define | AR5K_RATES_TURBO |

| #define | AR5K_RATES_XR |

| #define | c_channel channel |

| #define | c_channel_flags channelFlags |

| #define | HAL_SLOT_TIME_9 396 |

| #define | HAL_SLOT_TIME_20 880 |

| #define | HAL_SLOT_TIME_MAX 0xffff |

| #define | CHANNEL_A (IEEE80211_CHAN_5GHZ | IEEE80211_CHAN_OFDM) |

| #define | CHANNEL_B (IEEE80211_CHAN_2GHZ | IEEE80211_CHAN_CCK) |

| #define | CHANNEL_G (IEEE80211_CHAN_2GHZ | IEEE80211_CHAN_DYN) |

| #define | CHANNEL_PUREG (IEEE80211_CHAN_2GHZ | IEEE80211_CHAN_DYN) |

| #define | CHANNEL_T (CHANNEL_A | IEEE80211_CHAN_TURBO) |

| #define | CHANNEL_TG (CHANNEL_PUREG | IEEE80211_CHAN_TURBO) |

| #define | CHANNEL_XR (CHANNEL_A | IEEE80211_CHAN_XR) |

| #define | HAL_INT_RX 0x00000001 |

| #define | HAL_INT_RXDESC 0x00000002 |

| #define | HAL_INT_RXNOFRM 0x00000008 |

| #define | HAL_INT_RXEOL 0x00000010 |

| #define | HAL_INT_RXORN 0x00000020 |

| #define | HAL_INT_TX 0x00000040 |

| #define | HAL_INT_TXDESC 0x00000080 |

| #define | HAL_INT_TXURN 0x00000800 |

| #define | HAL_INT_MIB 0x00001000 |

| #define | HAL_INT_RXPHY 0x00004000 |

| #define | HAL_INT_RXKCM 0x00008000 |

| #define | HAL_INT_SWBA 0x00010000 |

| #define | HAL_INT_BMISS 0x00040000 |

| #define | HAL_INT_BNR 0x00100000 |

| #define | HAL_INT_GPIO 0x01000000 |

| #define | HAL_INT_FATAL 0x40000000 |

| #define | HAL_INT_GLOBAL 0x80000000 |

| #define | HAL_INT_NOCARD 0xffffffff |

| #define | HAL_INT_COMMON |

| #define | HAL_LED_INIT IEEE80211_S_INIT |

| #define | HAL_LED_SCAN IEEE80211_S_SCAN |

| #define | HAL_LED_AUTH IEEE80211_S_AUTH |

| #define | HAL_LED_ASSOC IEEE80211_S_ASSOC |

| #define | HAL_LED_RUN IEEE80211_S_RUN |

| #define | AR5K_GAIN_CRN_FIX_BITS_5111 4 |

| #define | AR5K_GAIN_CRN_FIX_BITS_5112 7 |

| #define | AR5K_GAIN_CRN_MAX_FIX_BITS AR5K_GAIN_CRN_FIX_BITS_5112 |

| #define | AR5K_GAIN_DYN_ADJUST_HI_MARGIN 15 |

| #define | AR5K_GAIN_DYN_ADJUST_LO_MARGIN 20 |

| #define | AR5K_GAIN_CCK_PROBE_CORR 5 |

| #define | AR5K_GAIN_CCK_OFDM_GAIN_DELTA 15 |

| #define | AR5K_GAIN_STEP_COUNT 10 |

| #define | AR5K_GAIN_PARAM_TX_CLIP 0 |

| #define | AR5K_GAIN_PARAM_PD_90 1 |

| #define | AR5K_GAIN_PARAM_PD_84 2 |

| #define | AR5K_GAIN_PARAM_GAIN_SEL 3 |

| #define | AR5K_GAIN_PARAM_MIX_ORN 0 |

| #define | AR5K_GAIN_PARAM_PD_138 1 |

| #define | AR5K_GAIN_PARAM_PD_137 2 |

| #define | AR5K_GAIN_PARAM_PD_136 3 |

| #define | AR5K_GAIN_PARAM_PD_132 4 |

| #define | AR5K_GAIN_PARAM_PD_131 5 |

| #define | AR5K_GAIN_PARAM_PD_130 6 |

| #define | AR5K_GAIN_CHECK_ADJUST(_g) ((_g)->g_current <= (_g)->g_low || (_g)->g_current >= (_g)->g_high) |

| #define | AR5K_AR5111_GAIN_OPT |

| #define | AR5K_AR5112_GAIN_OPT |

| #define | AR5K_EEPROM_MAGIC 0x003d |

| #define | AR5K_EEPROM_MAGIC_VALUE 0x5aa5 |

| #define | AR5K_EEPROM_PROTECT 0x003f |

| #define | AR5K_EEPROM_PROTECT_RD_0_31 0x0001 |

| #define | AR5K_EEPROM_PROTECT_WR_0_31 0x0002 |

| #define | AR5K_EEPROM_PROTECT_RD_32_63 0x0004 |

| #define | AR5K_EEPROM_PROTECT_WR_32_63 0x0008 |

| #define | AR5K_EEPROM_PROTECT_RD_64_127 0x0010 |

| #define | AR5K_EEPROM_PROTECT_WR_64_127 0x0020 |

| #define | AR5K_EEPROM_PROTECT_RD_128_191 0x0040 |

| #define | AR5K_EEPROM_PROTECT_WR_128_191 0x0080 |

| #define | AR5K_EEPROM_PROTECT_RD_192_207 0x0100 |

| #define | AR5K_EEPROM_PROTECT_WR_192_207 0x0200 |

| #define | AR5K_EEPROM_PROTECT_RD_208_223 0x0400 |

| #define | AR5K_EEPROM_PROTECT_WR_208_223 0x0800 |

| #define | AR5K_EEPROM_PROTECT_RD_224_239 0x1000 |

| #define | AR5K_EEPROM_PROTECT_WR_224_239 0x2000 |

| #define | AR5K_EEPROM_PROTECT_RD_240_255 0x4000 |

| #define | AR5K_EEPROM_PROTECT_WR_240_255 0x8000 |

| #define | AR5K_EEPROM_REG_DOMAIN 0x00bf |

| #define | AR5K_EEPROM_INFO_BASE 0x00c0 |

| #define | AR5K_EEPROM_INFO_MAX (0x400 - AR5K_EEPROM_INFO_BASE) |

| #define | AR5K_EEPROM_INFO(_n) (AR5K_EEPROM_INFO_BASE + (_n)) |

| #define | AR5K_EEPROM_VERSION AR5K_EEPROM_INFO(1) |

| #define | AR5K_EEPROM_VERSION_3_0 0x3000 |

| #define | AR5K_EEPROM_VERSION_3_1 0x3001 |

| #define | AR5K_EEPROM_VERSION_3_2 0x3002 |

| #define | AR5K_EEPROM_VERSION_3_3 0x3003 |

| #define | AR5K_EEPROM_VERSION_3_4 0x3004 |

| #define | AR5K_EEPROM_VERSION_4_0 0x4000 |

| #define | AR5K_EEPROM_VERSION_4_1 0x4001 |

| #define | AR5K_EEPROM_VERSION_4_2 0x4002 |

| #define | AR5K_EEPROM_VERSION_4_3 0x4003 |

| #define | AR5K_EEPROM_VERSION_4_6 0x4006 |

| #define | AR5K_EEPROM_VERSION_4_7 0x3007 |

| #define | AR5K_EEPROM_MODE_11A 0 |

| #define | AR5K_EEPROM_MODE_11B 1 |

| #define | AR5K_EEPROM_MODE_11G 2 |

| #define | AR5K_EEPROM_HDR AR5K_EEPROM_INFO(2) |

| #define | AR5K_EEPROM_HDR_11A(_v) (((_v) >> AR5K_EEPROM_MODE_11A) & 0x1) |

| #define | AR5K_EEPROM_HDR_11B(_v) (((_v) >> AR5K_EEPROM_MODE_11B) & 0x1) |

| #define | AR5K_EEPROM_HDR_11G(_v) (((_v) >> AR5K_EEPROM_MODE_11G) & 0x1) |

| #define | AR5K_EEPROM_HDR_T_2GHZ_DIS(_v) (((_v) >> 3) & 0x1) |

| #define | AR5K_EEPROM_HDR_T_5GHZ_DBM(_v) (((_v) >> 4) & 0x7f) |

| #define | AR5K_EEPROM_HDR_DEVICE(_v) (((_v) >> 11) & 0x7) |

| #define | AR5K_EEPROM_HDR_T_5GHZ_DIS(_v) (((_v) >> 15) & 0x1) |

| #define | AR5K_EEPROM_HDR_RFKILL(_v) (((_v) >> 14) & 0x1) |

| #define | AR5K_EEPROM_RFKILL_GPIO_SEL 0x0000001c |

| #define | AR5K_EEPROM_RFKILL_GPIO_SEL_S 2 |

| #define | AR5K_EEPROM_RFKILL_POLARITY 0x00000002 |

| #define | AR5K_EEPROM_RFKILL_POLARITY_S 1 |

| #define | AR5K_EEPROM_OFF(_v, _v3_0, _v3_3) (((_v) >= AR5K_EEPROM_VERSION_3_3) ? _v3_3 : _v3_0) |

| #define | AR5K_EEPROM_ANT_GAIN(_v) AR5K_EEPROM_OFF(_v, 0x00c4, 0x00c3) |

| #define | AR5K_EEPROM_ANT_GAIN_5GHZ(_v) ((int8_t)(((_v) >> 8) & 0xff)) |

| #define | AR5K_EEPROM_ANT_GAIN_2GHZ(_v) ((int8_t)((_v) & 0xff)) |

| #define | AR5K_EEPROM_MODES_11A(_v) AR5K_EEPROM_OFF(_v, 0x00c5, 0x00d4) |

| #define | AR5K_EEPROM_MODES_11B(_v) AR5K_EEPROM_OFF(_v, 0x00d0, 0x00f2) |

| #define | AR5K_EEPROM_MODES_11G(_v) AR5K_EEPROM_OFF(_v, 0x00da, 0x010d) |

| #define | AR5K_EEPROM_CTL(_v) AR5K_EEPROM_OFF(_v, 0x00e4, 0x0128) |

| #define | AR5K_EEPROM_OBDB0_2GHZ 0x00ec |

| #define | AR5K_EEPROM_OBDB1_2GHZ 0x00ed |

| #define | AR5K_EEPROM_MISC0 0x00c4 |

| #define | AR5K_EEPROM_EARSTART(_v) ((_v) & 0xfff) |

| #define | AR5K_EEPROM_EEMAP(_v) (((_v) >> 14) & 0x3) |

| #define | AR5K_EEPROM_MISC1 0x00c5 |

| #define | AR5K_EEPROM_TARGET_PWRSTART(_v) ((_v) & 0xfff) |

| #define | AR5K_EEPROM_HAS32KHZCRYSTAL(_v) (((_v) >> 14) & 0x1) |

| #define | AR5K_EEPROM_EEP_SCALE 100 |

| #define | AR5K_EEPROM_EEP_DELTA 10 |

| #define | AR5K_EEPROM_N_MODES 3 |

| #define | AR5K_EEPROM_N_5GHZ_CHAN 10 |

| #define | AR5K_EEPROM_N_2GHZ_CHAN 3 |

| #define | AR5K_EEPROM_MAX_CHAN 10 |

| #define | AR5K_EEPROM_N_PCDAC 11 |

| #define | AR5K_EEPROM_N_TEST_FREQ 8 |

| #define | AR5K_EEPROM_N_EDGES 8 |

| #define | AR5K_EEPROM_N_INTERCEPTS 11 |

| #define | AR5K_EEPROM_FREQ_M(_v) AR5K_EEPROM_OFF(_v, 0x7f, 0xff) |

| #define | AR5K_EEPROM_PCDAC_M 0x3f |

| #define | AR5K_EEPROM_PCDAC_START 1 |

| #define | AR5K_EEPROM_PCDAC_STOP 63 |

| #define | AR5K_EEPROM_PCDAC_STEP 1 |

| #define | AR5K_EEPROM_NON_EDGE_M 0x40 |

| #define | AR5K_EEPROM_CHANNEL_POWER 8 |

| #define | AR5K_EEPROM_N_OBDB 4 |

| #define | AR5K_EEPROM_OBDB_DIS 0xffff |

| #define | AR5K_EEPROM_CHANNEL_DIS 0xff |

| #define | AR5K_EEPROM_SCALE_OC_DELTA(_x) (((_x) * 2) / 10) |

| #define | AR5K_EEPROM_N_CTLS(_v) AR5K_EEPROM_OFF(_v, 16, 32) |

| #define | AR5K_EEPROM_MAX_CTLS 32 |

| #define | AR5K_EEPROM_N_XPD_PER_CHANNEL 4 |

| #define | AR5K_EEPROM_N_XPD0_POINTS 4 |

| #define | AR5K_EEPROM_N_XPD3_POINTS 3 |

| #define | AR5K_EEPROM_N_INTERCEPT_10_2GHZ 35 |

| #define | AR5K_EEPROM_N_INTERCEPT_10_5GHZ 55 |

| #define | AR5K_EEPROM_POWER_M 0x3f |

| #define | AR5K_EEPROM_POWER_MIN 0 |

| #define | AR5K_EEPROM_POWER_MAX 3150 |

| #define | AR5K_EEPROM_POWER_STEP 50 |

| #define | AR5K_EEPROM_POWER_TABLE_SIZE 64 |

| #define | AR5K_EEPROM_N_POWER_LOC_11B 4 |

| #define | AR5K_EEPROM_N_POWER_LOC_11G 6 |

| #define | AR5K_EEPROM_I_GAIN 10 |

| #define | AR5K_EEPROM_CCK_OFDM_DELTA 15 |

| #define | AR5K_EEPROM_N_IQ_CAL 2 |

| #define | AR5K_TXPOWER_OFDM(_r, _v) |

| #define | AR5K_TXPOWER_CCK(_r, _v) |

| #define | HAL_TXSTAT_ALTRATE 0x80 |

| #define | HAL_TXERR_XRETRY 0x01 |

| #define | HAL_TXERR_FILT 0x02 |

| #define | HAL_TXERR_FIFO 0x04 |

| #define | HAL_RXERR_CRC 0x01 |

| #define | HAL_RXERR_PHY 0x02 |

| #define | HAL_RXERR_FIFO 0x04 |

| #define | HAL_RXERR_DECRYPT 0x08 |

| #define | HAL_RXERR_MIC 0x10 |

| #define | HAL_RXKEYIX_INVALID ((u_int8_t) - 1) |

| #define | HAL_TXKEYIX_INVALID ((u_int32_t) - 1) |

| #define | HAL_PHYERR_UNDERRUN 0x00 |

| #define | HAL_PHYERR_TIMING 0x01 |

| #define | HAL_PHYERR_PARITY 0x02 |

| #define | HAL_PHYERR_RATE 0x03 |

| #define | HAL_PHYERR_LENGTH 0x04 |

| #define | HAL_PHYERR_RADAR 0x05 |

| #define | HAL_PHYERR_SERVICE 0x06 |

| #define | HAL_PHYERR_TOR 0x07 |

| #define | HAL_PHYERR_OFDM_TIMING 0x11 |

| #define | HAL_PHYERR_OFDM_SIGNAL_PARITY 0x12 |

| #define | HAL_PHYERR_OFDM_RATE_ILLEGAL 0x13 |

| #define | HAL_PHYERR_OFDM_LENGTH_ILLEGAL 0x14 |

| #define | HAL_PHYERR_OFDM_POWER_DROP 0x15 |

| #define | HAL_PHYERR_OFDM_SERVICE 0x16 |

| #define | HAL_PHYERR_OFDM_RESTART 0x17 |

| #define | HAL_PHYERR_CCK_TIMING 0x19 |

| #define | HAL_PHYERR_CCK_HEADER_CRC 0x1a |

| #define | HAL_PHYERR_CCK_RATE_ILLEGAL 0x1b |

| #define | HAL_PHYERR_CCK_SERVICE 0x1e |

| #define | HAL_PHYERR_CCK_RESTART 0x1f |

| #define | ds_rxstat ds_us.rx |

| #define | ds_txstat ds_us.tx |

| #define | HAL_RXDESC_INTREQ 0x0020 |

| #define | HAL_TXDESC_CLRDMASK 0x0001 |

| #define | HAL_TXDESC_NOACK 0x0002 |

| #define | HAL_TXDESC_RTSENA 0x0004 |

| #define | HAL_TXDESC_CTSENA 0x0008 |

| #define | HAL_TXDESC_INTREQ 0x0010 |

| #define | HAL_TXDESC_VEOL 0x0020 |

| #define | AR5K_HAL_FUNCTION(_hal, _n, _f) (_hal)->ah_##_f = ar5k_##_n##_##_f |

| #define | AR5K_HAL_FUNCTIONS(_t, _n, _a) |

| #define | AR5K_MAX_GPIO 10 |

| #define | AR5K_MAX_RF_BANKS 8 |

| #define | ah_getcountrycode ah_country_code |

| #define | ah_macVersion ah_mac_version |

| #define | ah_macRev ah_mac_revision |

| #define | ah_phyRev ah_phy_revision |

| #define | ah_analog5GhzRev ah_radio_5ghz_revision |

| #define | ah_analog2GhzRev ah_radio_2ghz_revision |

| #define | ah_regdomain ah_capabilities.reg_current |

| #define | ah_modes ah_capabilities.cap_mode |

| #define | ah_ee_version ah_capabilities.cap_eeprom.ee_version |

| #define | AR5K_SREV_NAME |

| #define | AR5K_SREV_UNKNOWN 0xffff |

| #define | AR5K_SREV_REV_FPGA 1 |

| #define | AR5K_SREV_REV_PROTO 2 |

| #define | AR5K_SREV_REV_PROTOA 3 |

| #define | AR5K_SREV_REV_AR5210 4 |

| #define | AR5K_SREV_REV_AR5210M 5 |

| #define | AR5K_SREV_REV_AR5210M23 7 |

| #define | AR5K_SREV_REV_AR521023 8 |

| #define | AR5K_SREV_VER_AR5210 0 |

| #define | AR5K_SREV_VER_AR5311 1 |

| #define | AR5K_SREV_VER_AR5311A 2 |

| #define | AR5K_SREV_VER_AR5311B 3 |

| #define | AR5K_SREV_VER_AR5211 4 |

| #define | AR5K_SREV_VER_AR5212 5 |

| #define | AR5K_SREV_RAD_5110 0x00 |

| #define | AR5K_SREV_RAD_5111 0x10 |

| #define | AR5K_SREV_RAD_5111A 0x15 |

| #define | AR5K_SREV_RAD_2111 0x20 |

| #define | AR5K_SREV_RAD_5112 0x30 |

| #define | AR5K_SREV_RAD_5112A 0x35 |

| #define | AR5K_SREV_RAD_2112 0x40 |

| #define | AR5K_SREV_RAD_2112A 0x45 |

| #define | HAL_ABI_VERSION 0x04090901 |

| #define | AR5K_PRINTF(fmt,) printk("%s: " fmt, __func__, ##__VA_ARGS__) |

| #define | AR5K_PRINT(fmt) printk("%s: " fmt, __func__) |

| #define | AR5K_TRACE |

| #define | AR5K_DELAY(_n) udelay(_n) |

| #define | bcopy(_a, _b, _c) memcpy(_b, _a, _c) |

| #define | bzero(_a, _b) memset(_a, 0, _b) |

| #define | printf AR5K_PRINT |

| #define | AR5K_ELEMENTS(_array) (sizeof(_array) / sizeof(_array[0])) |

| #define | AR5K_TUNE_DMA_BEACON_RESP 2 |

| #define | AR5K_TUNE_SW_BEACON_RESP 10 |

| #define | AR5K_TUNE_ADDITIONAL_SWBA_BACKOFF 0 |

| #define | AR5K_TUNE_RADAR_ALERT AH_FALSE |

| #define | AR5K_TUNE_MIN_TX_FIFO_THRES 1 |

| #define | AR5K_TUNE_MAX_TX_FIFO_THRES ((IEEE80211_MAX_LEN / 64) + 1) |

| #define | AR5K_TUNE_RSSI_THRES 1792 |

| #define | AR5K_TUNE_REGISTER_TIMEOUT 20000 |

| #define | AR5K_TUNE_REGISTER_DWELL_TIME 20000 |

| #define | AR5K_TUNE_BEACON_INTERVAL 100 |

| #define | AR5K_TUNE_AIFS 2 |

| #define | AR5K_TUNE_AIFS_11B 2 |

| #define | AR5K_TUNE_AIFS_XR 0 |

| #define | AR5K_TUNE_CWMIN 15 |

| #define | AR5K_TUNE_CWMIN_11B 31 |

| #define | AR5K_TUNE_CWMIN_XR 3 |

| #define | AR5K_TUNE_CWMAX 1023 |

| #define | AR5K_TUNE_CWMAX_11B 1023 |

| #define | AR5K_TUNE_CWMAX_XR 7 |

| #define | AR5K_TUNE_NOISE_FLOOR -72 |

| #define | AR5K_TUNE_MAX_TXPOWER 60 |

| #define | AR5K_TUNE_DEFAULT_TXPOWER 30 |

| #define | AR5K_TUNE_TPC_TXPOWER AH_TRUE |

| #define | AR5K_TUNE_ANT_DIVERSITY AH_TRUE |

| #define | AR5K_TUNE_HWTXTRIES 4 |

| #define | AR5K_TUNE_REGDOMAIN DMN_FCC1_FCCA |

| #define | AR5K_TUNE_CTRY CTRY_DEFAULT |

| #define | AR5K_INIT_MODE |

| #define | AR5K_INIT_TX_LATENCY 502 |

| #define | AR5K_INIT_USEC 39 |

| #define | AR5K_INIT_USEC_TURBO 79 |

| #define | AR5K_INIT_USEC_32 31 |

| #define | AR5K_INIT_CARR_SENSE_EN 1 |

| #define | AR5K_INIT_PROG_IFS 920 |

| #define | AR5K_INIT_PROG_IFS_TURBO 960 |

| #define | AR5K_INIT_EIFS 3440 |

| #define | AR5K_INIT_EIFS_TURBO 6880 |

| #define | AR5K_INIT_SLOT_TIME 396 |

| #define | AR5K_INIT_SLOT_TIME_TURBO 480 |

| #define | AR5K_INIT_ACK_CTS_TIMEOUT 1024 |

| #define | AR5K_INIT_ACK_CTS_TIMEOUT_TURBO 0x08000800 |

| #define | AR5K_INIT_SIFS 560 |

| #define | AR5K_INIT_SIFS_TURBO 480 |

| #define | AR5K_INIT_SH_RETRY 10 |

| #define | AR5K_INIT_LG_RETRY AR5K_INIT_SH_RETRY |

| #define | AR5K_INIT_SSH_RETRY 32 |

| #define | AR5K_INIT_SLG_RETRY AR5K_INIT_SSH_RETRY |

| #define | AR5K_INIT_TX_RETRY 10 |

| #define | AR5K_INIT_TOPS 8 |

| #define | AR5K_INIT_RXNOFRM 8 |

| #define | AR5K_INIT_RPGTO 0 |

| #define | AR5K_INIT_TXNOFRM 0 |

| #define | AR5K_INIT_BEACON_PERIOD 65535 |

| #define | AR5K_INIT_TIM_OFFSET 0 |

| #define | AR5K_INIT_BEACON_EN 0 |

| #define | AR5K_INIT_RESET_TSF 0 |

| #define | AR5K_INIT_TRANSMIT_LATENCY |

| #define | AR5K_INIT_TRANSMIT_LATENCY_TURBO |

| #define | AR5K_INIT_PROTO_TIME_CNTRL |

| #define | AR5K_INIT_PROTO_TIME_CNTRL_TURBO |

| #define | AR5K_INIT_BEACON_CONTROL |

| #define | __bswap32(_x) (_x) |

| #define | AR5K_REG_WRITE(_reg, _val) (writel(cpu_to_le32(_val), hal->ah_sh + (_reg))) |

| #define | AR5K_REG_READ(_reg) (le32_to_cpu(readl(hal->ah_sh + (_reg)))) |

| #define | AR5K_REG_SM(_val, _flags) (((_val) << _flags##_S) & (_flags)) |

| #define | AR5K_REG_MS(_val, _flags) (((_val) & (_flags)) >> _flags##_S) |

| #define | AR5K_REG_WRITE_BITS(_reg, _flags, _val) |

| #define | AR5K_REG_MASKED_BITS(_reg, _flags, _mask) AR5K_REG_WRITE(_reg, (AR5K_REG_READ(_reg) & (_mask)) | (_flags)) |

| #define | AR5K_REG_ENABLE_BITS(_reg, _flags) AR5K_REG_WRITE(_reg, AR5K_REG_READ(_reg) | (_flags)) |

| #define | AR5K_REG_DISABLE_BITS(_reg, _flags) AR5K_REG_WRITE(_reg, AR5K_REG_READ(_reg) &~ (_flags)) |

| #define | AR5K_PHY_WRITE(_reg, _val) AR5K_REG_WRITE(hal->ah_phy + ((_reg) << 2), _val) |

| #define | AR5K_PHY_READ(_reg) AR5K_REG_READ(hal->ah_phy + ((_reg) << 2)) |

| #define | AR5K_REG_WAIT(_i) |

| #define | AR5K_EEPROM_READ(_o, _v) |

| #define | AR5K_EEPROM_READ_HDR(_o, _v) AR5K_EEPROM_READ(_o, hal->ah_capabilities.cap_eeprom._v); \ |

| #define | AR5K_REG_READ_Q(_reg, _queue) (AR5K_REG_READ(_reg) & (1 << _queue)) \ |

| #define | AR5K_REG_WRITE_Q(_reg, _queue) AR5K_REG_WRITE(_reg, (1 << _queue)) |

| #define | AR5K_Q_ENABLE_BITS(_reg, _queue) |

| #define | AR5K_Q_DISABLE_BITS(_reg, _queue) |

| #define | AR5K_LE_READ_2(_p) (((const u_int8_t *)(_p))[0] | (((const u_int8_t *)(_p))[1] << 8)) |

| #define | AR5K_LE_READ_4(_p) |

| #define | AR5K_LE_WRITE_2(_p, _val) |

| #define | AR5K_LE_WRITE_4(_p, _val) |

| #define | AR5K_INI_VAL_11A 0 |

| #define | AR5K_INI_VAL_11A_TURBO 1 |

| #define | AR5K_INI_VAL_11B 2 |

| #define | AR5K_INI_VAL_11G 3 |

| #define | AR5K_INI_VAL_11G_TURBO 4 |

| #define | AR5K_INI_VAL_XR 0 |

| #define | AR5K_INI_VAL_MAX 5 |

| #define | AR5K_INI_PHY_5111 0 |

| #define | AR5K_INI_PHY_5112 1 |

| #define | AR5K_INI_PHY_511X 1 |

| #define | AR5K_AR5111_INI_RF_MAX_BANKS AR5K_MAX_RF_BANKS |

| #define | AR5K_AR5112_INI_RF_MAX_BANKS AR5K_MAX_RF_BANKS |

| #define | AR5K_AR5111_INI_RF |

| #define | AR5K_AR5112_INI_RF |

| #define | AR5K_INI_RFGAIN_5GHZ 0 |

| #define | AR5K_INI_RFGAIN_2GHZ 1 |

| #define | AR5K_INI_RFGAIN |

Typedefs |

| typedef void * | HAL_SOFTC |

| typedef int | HAL_BUS_TAG |

| typedef void * | HAL_BUS_HANDLE |

| typedef u_int32_t | HAL_BUS_ADDR |

| typedef int | HAL_STATUS |

| typedef uint32_t | HAL_CTRY_CODE |

| typedef u_int32_t | HAL_INT |

| typedef enum ieee80211_state | HAL_LED_STATE |

| typedef ath_hal *() | ar5k_attach_t (u_int16_t, void *, HAL_BUS_TAG, HAL_BUS_HANDLE, HAL_STATUS *) |

| typedef HAL_BOOL() | ar5k_rfgain_t (struct ath_hal *, HAL_CHANNEL *, u_int) |

Enumerations |

| enum | ar5k_version { AR5K_AR5210 = 0, AR5K_AR5211 = 1, AR5K_AR5212 = 2 } |

| enum | ar5k_radio { AR5K_AR5110 = 0, AR5K_AR5111 = 1, AR5K_AR5112 = 2 } |

| enum | HAL_BOOL { AH_FALSE = 0, AH_TRUE } |

| enum | HAL_MODE {

HAL_MODE_11A = 0x001, HAL_MODE_TURBO = 0x002, HAL_MODE_11B = 0x004, HAL_MODE_PUREG = 0x008,

HAL_MODE_11G = 0x008, HAL_MODE_108G = 0x020, HAL_MODE_XR = 0x040, HAL_MODE_ALL = 0xfff

} |

| enum | HAL_ANT_SETTING { HAL_ANT_VARIABLE = 0, HAL_ANT_FIXED_A = 1, HAL_ANT_FIXED_B = 2, HAL_ANT_MAX = 3 } |

| enum | HAL_OPMODE { HAL_M_STA = 1, HAL_M_IBSS = 0, HAL_M_HOSTAP = 6, HAL_M_MONITOR = 8 } |

| enum | HAL_TX_QUEUE {

HAL_TX_QUEUE_INACTIVE = 0, HAL_TX_QUEUE_DATA, HAL_TX_QUEUE_BEACON, HAL_TX_QUEUE_CAB,

HAL_TX_QUEUE_PSPOLL

} |

| enum | HAL_TX_QUEUE_ID {

HAL_TX_QUEUE_ID_DATA_MIN = 0, HAL_TX_QUEUE_ID_DATA_MAX = 6, HAL_TX_QUEUE_ID_PSPOLL = 7, HAL_TX_QUEUE_ID_BEACON = 8,

HAL_TX_QUEUE_ID_CAB = 9

} |

| enum | HAL_TX_QUEUE_SUBTYPE {

HAL_WME_AC_BK = 0, HAL_WME_AC_BE = 1, HAL_WME_AC_VI = 2, HAL_WME_AC_VO = 3,

HAL_WME_UPSD = 4

} |

| enum | HAL_PKT_TYPE {

HAL_PKT_TYPE_NORMAL = 0, HAL_PKT_TYPE_ATIM = 1, HAL_PKT_TYPE_PSPOLL = 2, HAL_PKT_TYPE_BEACON = 3,

HAL_PKT_TYPE_PROBE_RESP = 4, HAL_PKT_TYPE_PIFS = 5

} |

| enum | HAL_POWER_MODE {

HAL_PM_UNDEFINED = 0, HAL_PM_AUTO, HAL_PM_AWAKE, HAL_PM_FULL_SLEEP,

HAL_PM_NETWORK_SLEEP

} |

| enum | HAL_CIPHER {

HAL_CIPHER_WEP = 0, HAL_CIPHER_AES_OCB, HAL_CIPHER_AES_CCM, HAL_CIPHER_CKIP,

HAL_CIPHER_TKIP, HAL_CIPHER_CLR, HAL_CIPHER_MIC

} |

| enum | HAL_CAPABILITY_TYPE {

HAL_CAP_PHYCOUNTERS, HAL_CAP_CIPHER, HAL_CAP_TKIP_SPLIT, HAL_CAP_TPC,

HAL_CAP_TXPOW, HAL_CAP_BURST, HAL_CAP_DIVERSITY, HAL_CAP_VEOL,

HAL_CAP_REG_DMN, HAL_CAP_NUM_TXQUEUES

} |

| enum | HAL_RFGAIN { HAL_RFGAIN_INACTIVE = 0, HAL_RFGAIN_READ_REQUESTED, HAL_RFGAIN_NEED_CHANGE } |

| enum | HAL_CHIP { HAL_CHIP_5GHZ = IEEE80211_CHAN_5GHZ, HAL_CHIP_2GHZ = IEEE80211_CHAN_2GHZ } |

| enum | ar5k_srev_type { AR5K_VERSION_VER, AR5K_VERSION_REV, AR5K_VERSION_RAD } |

Functions |

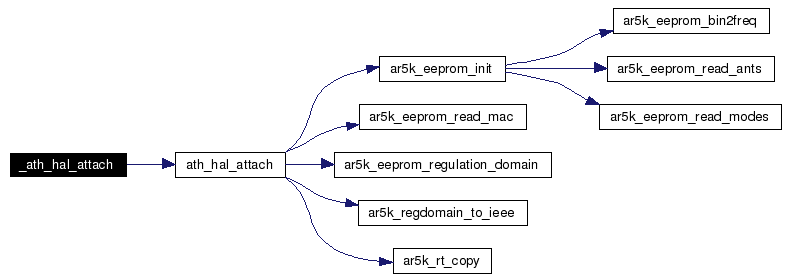

| const char * | ath_hal_probe (u_int16_t, u_int16_t) |

| ath_hal * | _ath_hal_attach (u_int16_t devid, HAL_SOFTC sc, HAL_BUS_TAG t, HAL_BUS_HANDLE h, void *s) |

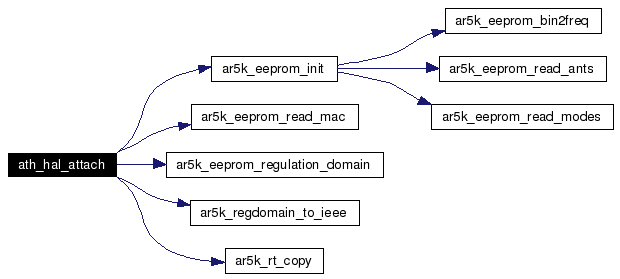

| ath_hal * | ath_hal_attach (u_int16_t device, HAL_SOFTC sc, HAL_BUS_TAG, HAL_BUS_HANDLE, HAL_STATUS *) |

| void | ath_hal_detach (struct ath_hal *ah) |

| u_int16_t | ath_hal_computetxtime (struct ath_hal *, const HAL_RATE_TABLE *, u_int32_t, u_int16_t, HAL_BOOL) |

| u_int | ath_hal_mhz2ieee (u_int, u_int) |

| u_int | ath_hal_ieee2mhz (u_int, u_int) |

| HAL_BOOL | ath_hal_init_channels (struct ath_hal *, HAL_CHANNEL *, u_int, u_int *, HAL_CTRY_CODE, u_int16_t, HAL_BOOL, HAL_BOOL) |

| u_int | ath_hal_getwirelessmodes (struct ath_hal *, HAL_CTRY_CODE) |

| const char * | ar5k_printver (enum ar5k_srev_type, u_int) |

| void | ar5k_radar_alert (struct ath_hal *) |

| u_int32_t | ar5k_regdomain_to_ieee (u_int16_t) |

| u_int16_t | ar5k_regdomain_from_ieee (u_int32_t) |

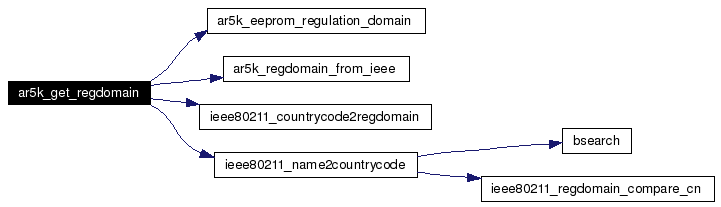

| u_int16_t | ar5k_get_regdomain (struct ath_hal *) |

| u_int32_t | ar5k_bitswap (u_int32_t, u_int) |

| u_int | ar5k_clocktoh (u_int, HAL_BOOL) |

| u_int | ar5k_htoclock (u_int, HAL_BOOL) |

| void | ar5k_rt_copy (HAL_RATE_TABLE *, const HAL_RATE_TABLE *) |

| HAL_BOOL | ar5k_register_timeout (struct ath_hal *, u_int32_t, u_int32_t, u_int32_t, HAL_BOOL) |

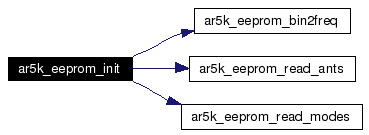

| int | ar5k_eeprom_init (struct ath_hal *) |

| int | ar5k_eeprom_read_mac (struct ath_hal *, u_int8_t *) |

| HAL_BOOL | ar5k_eeprom_regulation_domain (struct ath_hal *, HAL_BOOL, u_int32_t *) |

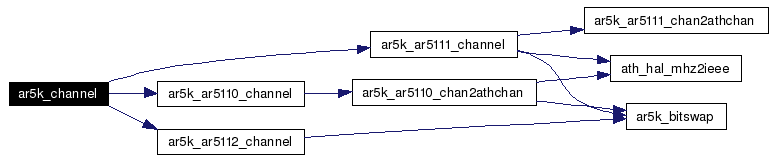

| HAL_BOOL | ar5k_channel (struct ath_hal *, HAL_CHANNEL *) |

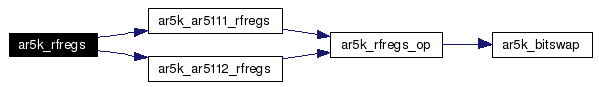

| HAL_BOOL | ar5k_rfregs (struct ath_hal *, HAL_CHANNEL *, u_int) |

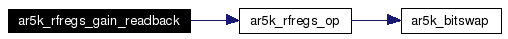

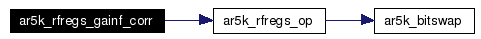

| u_int32_t | ar5k_rfregs_gainf_corr (struct ath_hal *) |

| HAL_BOOL | ar5k_rfregs_gain_readback (struct ath_hal *) |

| int32_t | ar5k_rfregs_gain_adjust (struct ath_hal *) |

| HAL_BOOL | ar5k_rfgain (struct ath_hal *, u_int, u_int) |

| void | ar5k_txpower_table (struct ath_hal *, HAL_CHANNEL *, int16_t) |

Variables |

| ath_desc | __packed__ |

| | Value: { 12, { \

255, 255, 255, 255, 255, 255, 255, 255, 10, 8, 6, 4, \

11, 9, 7, 5, 255, 255, 255, 255, 255, 255, 255, 255, \

3, 2, 1, 0, 255, 255, 255, 255 }, { \

{ 1, IEEE80211_T_CCK, 1000, 27, 0x00, 2, 0 }, \

{ 1, IEEE80211_T_CCK, 2000, 26, 0x04, 4, 1 }, \

{ 1, IEEE80211_T_CCK, 5500, 25, 0x04, 11, 1 }, \

{ 1, IEEE80211_T_CCK, 11000, 24, 0x04, 22, 1 }, \

{ 0, IEEE80211_T_OFDM, 6000, 11, 0, 12, 4 }, \

{ 0, IEEE80211_T_OFDM, 9000, 15, 0, 18, 4 }, \

{ 1, IEEE80211_T_OFDM, 12000, 10, 0, 24, 6 }, \

{ 1, IEEE80211_T_OFDM, 18000, 14, 0, 36, 6 }, \

{ 1, IEEE80211_T_OFDM, 24000, 9, 0, 48, 8 }, \

{ 1, IEEE80211_T_OFDM, 36000, 13, 0, 72, 8 }, \

{ 1, IEEE80211_T_OFDM, 48000, 8, 0, 96, 8 }, \

{ 1, IEEE80211_T_OFDM, 54000, 12, 0, 108, 8 } } \

}

Definition at line 416 of file ah.h. |

| | Value: { 12, { \

255, 3, 1, 255, 255, 255, 2, 0, 10, 8, 6, 4, \

11, 9, 7, 5, 255, 255, 255, 255, 255, 255, 255, 255, \

255, 255, 255, 255, 255, 255, 255, 255 }, { \

{ 1, IEEE80211_T_XR, 500, 7, 0, 129, 0 }, \

{ 1, IEEE80211_T_XR, 1000, 2, 0, 139, 1 }, \

{ 1, IEEE80211_T_XR, 2000, 6, 0, 150, 2 }, \

{ 1, IEEE80211_T_XR, 3000, 1, 0, 150, 3 }, \

{ 1, IEEE80211_T_OFDM, 6000, 11, 0, 140, 4 }, \

{ 1, IEEE80211_T_OFDM, 9000, 15, 0, 18, 4 }, \

{ 1, IEEE80211_T_OFDM, 12000, 10, 0, 152, 6 }, \

{ 1, IEEE80211_T_OFDM, 18000, 14, 0, 36, 6 }, \

{ 1, IEEE80211_T_OFDM, 24000, 9, 0, 176, 8 }, \

{ 1, IEEE80211_T_OFDM, 36000, 13, 0, 72, 8 }, \

{ 1, IEEE80211_T_OFDM, 48000, 8, 0, 96, 8 }, \

{ 1, IEEE80211_T_OFDM, 54000, 12, 0, 108, 8 } } \

}

Definition at line 448 of file ah.h. |

1.4.1

1.4.1